SystemX Affiliates: login to view related content.

This panel's intent is to review and discuss the past, present and especilally the future for the fabless model of semiconductor development. There will be 3 short presentations followed by a moderated q&a.

- Paul Franklin will drawn upon his extensive experience in Silicon Valley to bring us to the present. His talk will discuss the evolution of our industry, and now its growing consolidation.

- Mike Gianfagna, with his perspective anchored in eSilicon, will talk to the emerging model of cloud-based tools, shared fab access and shared logistics management, all keeping the door open to ASIC development for the small to modest scale end product, as well as, for fabless semiconductor companies more generally.

- Victor Peng, from Xilinx, will present the alternative model of repurposing of high volume but configurable standard products/platforms. FPGA's, and their programmable platform brethren: PSoCs/MPSoCs represent a faster and more developmentally economical manner of semiconductor product realization.

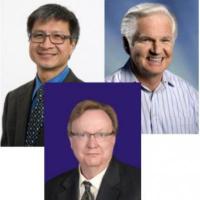

Our three panelists/speakers:

Victor Peng is the Executive Vice President & General Manager of Products at Xilinx. In this role, he leads the product definition and marketing groups, and the silicon, software, IP, and technology engineering teams for the company. Before joining Xilinx, Mr. Peng served as corporate vice president of the graphics products group (GPG) silicon engineering with AMD, where he also was a key leader for the company's central silicon engineering team supporting graphics, console game products, CPU chipset and consumer business units. Previously, he held key engineering leadership roles at TZero Technologies, MIPS Technologies, SGI and Digital Equipment Corp. Mr. Peng earned a BSEE from Rensselaer Polytechnic Institute and an M.Eng. in Electrical Engineering from Cornell University.

Paul Franklin, former Vice President of Operations at Atheros from 2003-2009 (acquired by Qualcomm in 2011) has over 50 years in the semiconductor business. From 2001 to 2003 he served as an independent consultant in the semiconductor industry focusing on operations, business planning, financing and as a CEO at Inphi Corporation. He was President of the Multimedia Products Division of SonicBlue, formerly S3 Corporation from 1999 through 2000, after the acquisition of Diamond Multimedia. Earlier at S3, a fabless graphics semiconductor company, he had served as Senior Vice President of Operations from 1992. Prior to that he was Vice President of Operations and helped start up Actel, an FPGA supplier and one of the earliest Fabless companies in 1985. He spent another 20 years in management, engineering roles in manufacturing, product engineering, strategic marketing, business development and R&QA functions at Monolithic Memories Inc. (acquired by AMD), Motorola and Dickson Electronics (acquired by Siemens). Mr. Franklin majored in chemistry at Brooklyn Polytechnic Institute (now Polytechnic Institute of New York) and Arizona State University. He was an early member of the Bay Area Band of Angels and has served on a number of BODs and advisory board positions. He continues as an advisor to start-ups and venture capital firms.

Mike Gianfagna is currently Vice President of Marketing at eSilicon Corporation. He has over 30 years of business and technology experience in semiconductors and EDA. Prior to eSilicon, Mr. Gianfagna was vice president of corporate marketing at Atrenta, Inc., now part of Synopsys. Prior to Atrenta, he was president and CEO of Aprio Technologies, a venture-funded design-for-manufacturability startup. Before Aprio, he was an early employee of eSilicon Corporation. Mr. Gianfagna has also held senior management positions at Cadence Design Systems, Zycad Corporation, General Electric and Harris Semiconductor (now Intersil). His career began at RCA Solid State, where he was part of the team that launched the company’s ASIC business. Mr Gianfagna holds a Bachelor of Science in Electrical Engineering from New York University and a Master of Science in Electrical Engineering from Rutgers University.